[HostHum.com] 7 月 27 日消息,Intel 在太平洋夏令时间 7 月 26 日下午两点(北京时间 27 日凌晨四点)的线上发布会中,介绍了英特尔未来的制程工艺和封装技术线路图。

本次线上发布会以 “Intel Accelerated”(英特尔加速创新)为主题。Intel CEO 帕特·基辛格(Pat Gelsinger)在会中表示:“基于英特尔在芯片封装领域毋庸置疑的领先性,我们正在加快制程工艺的创新,以确保到 2025 年制程性能再度领先业界。英特尔正利用我们无可比拟的持续创新能力,实现从晶体管到系统层面的全面技术进步。在穷尽元素周期表之前,我们将继续追寻摩尔定律,利用硅的神奇力量不断创新。”

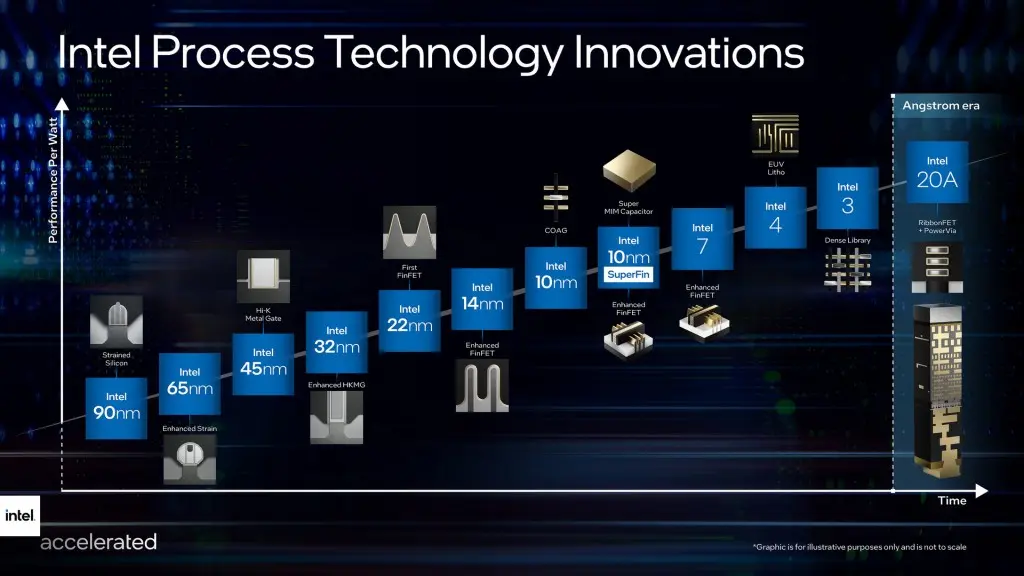

会上,Intel 揭晓了到 2025 年的最新制程与封装技术发展蓝图,不仅引入了全新的制程命名方式,还同步发表了全新的电晶体架构 RibbonFET 和业界首款背部供电方案 PowerVia。

(图片来源: intel.com)

而未来将以制程节点的每瓦效能为基准,导入全新命名方式,也让客户更易于识别:

| 制程节点 | 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| 目标 | - | 原名 10nm SuperFi | 原名 7nm | 供电、面积效率强化 | 进入 A 时代 | 未定 |

| 每瓦性能提升 | - | 10-15% | 20% | 18% | 未定 | 未定 |

| 状态 | 已大量生产 | 进入量产阶段 | 2022 下半年投产 | 2023 下半年投产 | 2024 上半年投产 | 2025 投产 |

| 产品 | Tiger Lake | Alder Lake | Meteor Lake | 未定 | 未定 | 未定 |

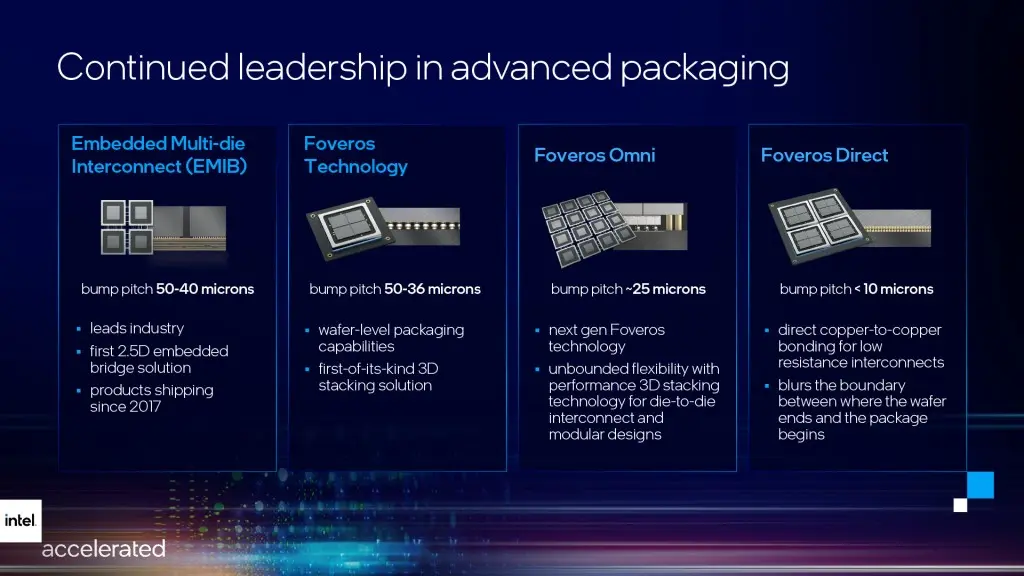

Intel 封装技术发展蓝图

- 英特尔自 2017 年以来一直在出货 EMIB 产品,EMIB 作为首个 2.5D 嵌入式桥接解决方案将继续引领行业;

- Foveros 利用晶圆级封装能力,提供史上首个 3D 堆叠解决方案;

- Foveros Omni 开创了下一代 Foveros 技术,通过高性能3D堆叠技术为裸片到裸片的互连和模块化设计提供了无限制的灵活性;

- Foveros Direct 实现了向直接铜对铜键合的转变,它可以实现低电阻互连,并使得从晶圆制成到封装开始,两者之间的界限不再那么截然。

本次发布会还有一个重点是 Intel 成立了代工服务部门,并计划计划使用即将于 2024 年发布的 20A 制程工艺为高通生产芯片。目前,三星正在为高通制造部分骁龙处理器。数十年来,英特尔在制造最小、最快的计算芯片技术方面一直处于领先地位,但如今优势已经被台积电和三星夺走,因此 Intel 正在扩大新的代工业务,以实现在 2025 年前追赶上台积电和三星电子等竞争对手的目标。